【CNMO科技音书】CNMO从韩媒获悉,三星电子在DRAM制造技巧方面获得打破,初次告捷产出10纳米以下级别的责任晶圆。这一发达记号着该公司在克服DRAM“10纳米魔咒”方面迈出了要津一步。 据业界音书,三星电子上月坐蓐了承袭10a工艺的晶圆,并在芯片特点检测经由中说明了责任晶圆的存在。这是该公司初次利用4F平地契位结构和垂纵贯谈晶体督工艺的遵守。在DRAM行业,10纳米级别工艺频繁按1x、1y、1z、1a、1b、1c、1d的规矩分辨代际。10a代表1d之后的下一代,是首个低于10纳米的节点。

【CNMO科技音书】CNMO从韩媒获悉,三星电子在DRAM制造技巧方面获得打破,初次告捷产出10纳米以下级别的责任晶圆。这一发达记号着该公司在克服DRAM“10纳米魔咒”方面迈出了要津一步。

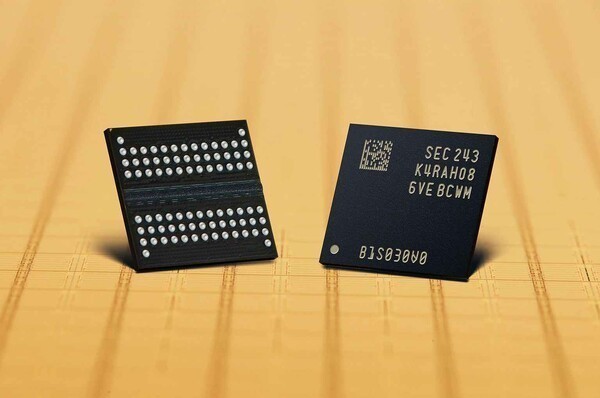

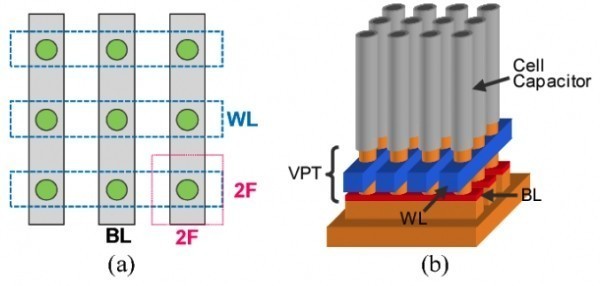

据业界音书,三星电子上月坐蓐了承袭10a工艺的晶圆,并在芯片特点检测经由中说明了责任晶圆的存在。这是该公司初次利用4F平地契位结构和垂纵贯谈晶体督工艺的遵守。在DRAM行业,10纳米级别工艺频繁按1x、1y、1z、1a、1b、1c、1d的规矩分辨代际。10a代表1d之后的下一代,是首个低于10纳米的节点。行家分析其内容电阶梯宽约为9.5至9.7纳米水平。

干系报谈

责任晶圆是指从晶圆上切割下来的芯片中大略按遐想普通运作的部分。在开垦阶段产出责任晶圆,被视为遐想与工艺认识正确的信号,之后将进行良率提高和可靠性考证等后续责任。三星电子打算本年完成基于此结构的10a DRAM开垦,来岁进行质地测试,并于2028年将其鬈曲到量产坐蓐线。该公司打算在10a、10b、10c三个代际中使用4F平方和VCT结构,并从10d开动转向3D DRAM。

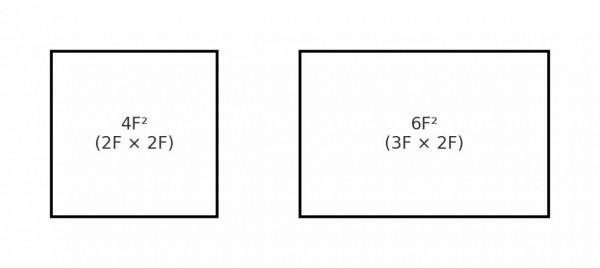

这次打破的要津在于承袭了4F平地契位面积和垂纵贯谈晶体管这两项新技巧。此前DRAM单位面积为6F平方,而10a工艺将其松开至4F平方。表面标明,在相似的芯片尺寸下,转向4F平方结构可容纳30%至50%更多的单位,成心于提高容量、速率并裁减功耗。为了在松开后的单位面积上嘱托栅极、通谈和电容器,三星引入了VCT技巧。该技巧将电容器置于晶体管上方,篡改了以往两者各自占用单位面积的传统布局。

跟着4F平方和VCT技巧的利用,中枢材料也随之篡改。三星电子将通谈材料从硅改为铟镓锌氧化物,以在松开单位中扼制泄走电流并确保数据保抓特点。此外,在单位周围布局的各式外围电路将承袭单独晶圆加工,并通过晶圆对晶圆搀杂键合技巧集结的PUC有筹备。

业界东谈主士指出,三星电子这次告捷产出责任晶圆,意味着承袭该技巧的开垦与量产责任将加快鼓动。与此同期世界杯体育,其他厂商的计谋有所不同。好意思光打算尽可能保管现存遐想。中国DRAM厂商由于无法入口极紫外光刻诞生,在近况下难以进行线宽松开,因此正积极开垦3D DRAM,合计一朝DRAM竣事3D化,便可使用传统光刻诞生制造先进居品。SK海力士则打算在10b节点而非10a节点利用4F平方和VCT技巧。